## **Table of Contents**

| 1.0  | Introduction                                                     |      |

|------|------------------------------------------------------------------|------|

| 1.1  | Description                                                      |      |

| 1.2  | Board Features                                                   | 5    |

| 1.3  | Test Files                                                       |      |

| 1.4  | Reference Designs                                                | 6    |

| 1.5  | Ordering Information                                             | 6    |

| 2.0  | Functional Description                                           | 7    |

| 2.1  | Xilinx Virtex-5 LXT/SXT FPGA                                     | 8    |

| 2.2  | GTP Interface                                                    |      |

| 2.   | 2.1 GTP Reference Clock Inputs                                   | . 10 |

| 2.   | 2.2 PCI Express x8 Add-in Card                                   | . 10 |

| 2.   | 2.3 SFP Connectors                                               |      |

| 2.   | 2.4 Serial ATA Connector                                         |      |

| 2.   | 2.5 GTP on EXP Connector JX1                                     | . 15 |

| 2.   | 2.6 10 Gb/s Media Connector                                      | . 15 |

| 2.3  | Memory                                                           |      |

| 2.   | 3.1 DDR2 SDRAM Interface                                         | . 17 |

| 2.   | 3.2 DDR2 SODIMM Interface (LX110T/SX95T Only)                    | . 19 |

| 2.   | 3.3 Flash Interface                                              | . 22 |

| 2.4  | Clock Sources                                                    | .23  |

| 2.   | 4.1 ICS8442 Programmable LVDS Clock Synthesizer                  |      |

| 2.   | 4.1.1 ICS8442 Člock Generation                                   |      |

| 2.   | 4.1.2 ICS8442 M and N Settings                                   |      |

| 2.5  | Communication                                                    |      |

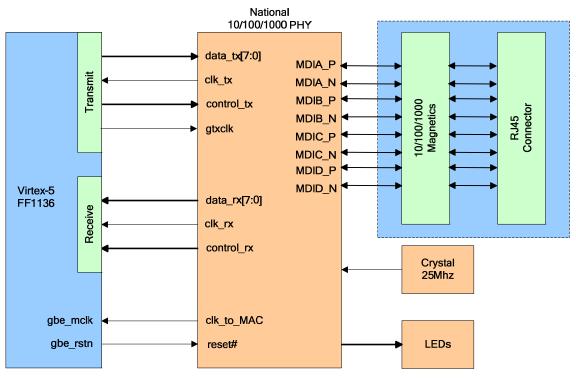

| 2.   | 5.1 10/100/1000 Ethernet PHY                                     |      |

| 2.   | 5.2 Universal Serial Bus (USB)                                   |      |

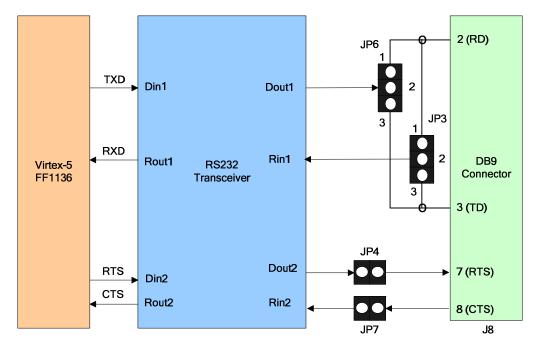

| 2.   | 5.3 RS232                                                        |      |

| 2.6  | User Switches                                                    |      |

| 2.7  | User LEDs                                                        |      |

| 2.8  | Configuration                                                    |      |

| 2.   | 8.1 Configuration Modes                                          |      |

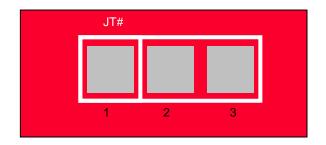

| 2.   | 8.2 JTAG Chain                                                   |      |

|      | 8.3 Byte Peripheral Interface (BPI)                              |      |

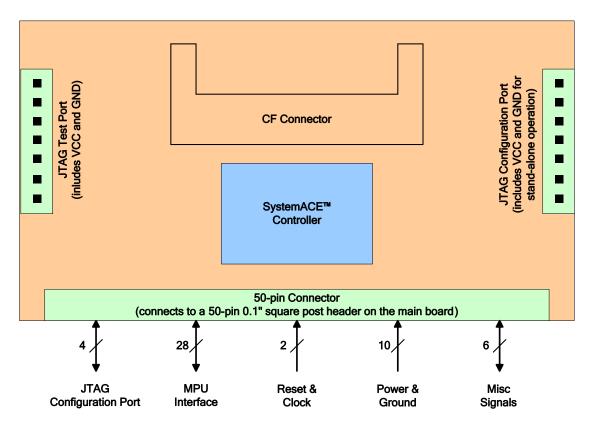

|      | 8.4 System ACE Module Connector                                  |      |

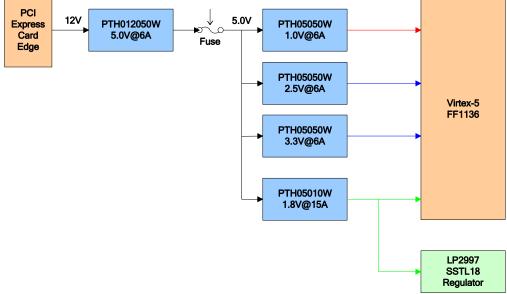

| 2.9  | Power                                                            | .38  |

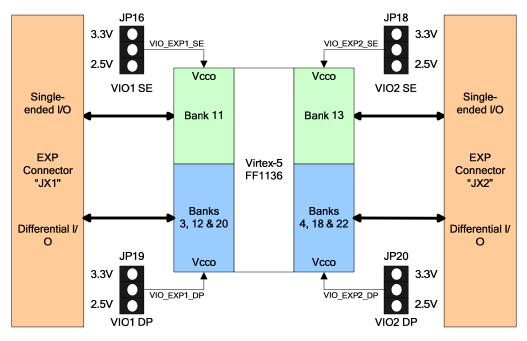

| 2.   | 9.1 FPGA I/O Voltage (Vcco)                                      |      |

|      | 9.2 FPGA Reference Voltage (Vref)                                |      |

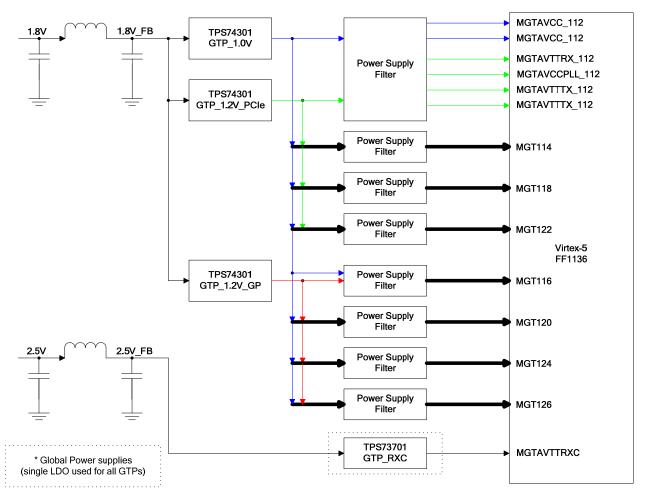

| 2.   | 9.3 GTP Voltage Regulators (AVCC, AVCCPLL, VTTRX, VTTTX, VTTRXC) | .40  |

| 2.10 |                                                                  | .41  |

| 2.   | 10.1 Passive Heat Sink                                           | .41  |

|      | 10.2 Active Heat Sink Support                                    |      |

| 2.11 | Expansion Connectors                                             |      |

|      | 11.1 EXP Interface                                               |      |

| 3.0  | Test Designs                                                     |      |

| 3.1  | PCI Express PIO Example                                          |      |

| 3.2  | Ethernet Test                                                    |      |

| 3.3  | Factory Test                                                     |      |

| 4.0  | Revisions                                                        |      |

|      |                                                                  |      |

# **Figures**

| Figure 1 - Virtex-5 LXT/SXT PCI Express Board Picture                         | 6  |

|-------------------------------------------------------------------------------|----|

| Figure 2 - Virtex-5 LXT/SXT PCI Express Board Block Diagram                   | 7  |

| Figure 3 - GTP Ports on the Virtex-5 PCI Express Board                        | 9  |

| Figure 4 - GTP Clock Sources on the Virtex-5 PCI Express Board                | 10 |

| Figure 5 - PCI Express x8 Interface                                           | 11 |

| Figure 6 - SFP Module Interfaces                                              |    |

| Figure 7 - Host Board Connector AMP 1367073-1 (photo taken from AMP Web Page) | 14 |

| Figure 8 - 10 Gb/s Media Connector Interface                                  | 16 |

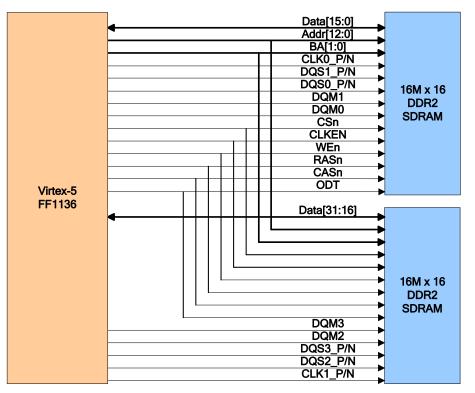

| Figure 9 - DDR2 SDRAM Interface                                               | 17 |

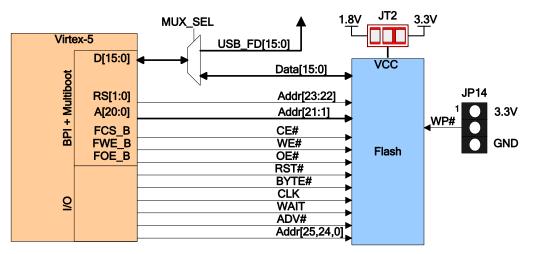

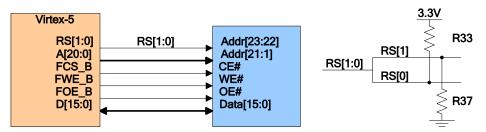

| Figure 10 - Flash Interface                                                   |    |

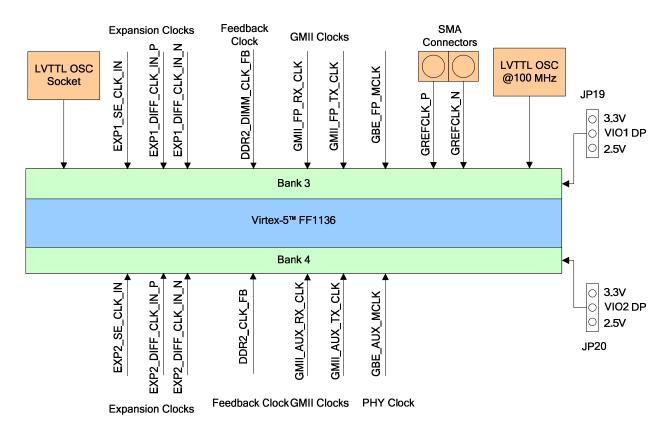

| Figure 11 - Clock Nets Connected to Global Clock Inputs                       |    |

| Figure 12 - ICS8442 Clock Synthesizer                                         | 25 |

| Figure 13 - ICS8442 Clock Synthesizer Interface to the FPGA                   |    |

| Figure 14 - ICS8442 Clock Synthesizer M and N DIP Switches                    |    |

| Figure 15 - M and N DIP Switches for the Synthesizers                         |    |

| Figure 16 - 10/100/1000 Mb/s Ethernet Interface                               |    |

| Figure 17 - RS232 Interface                                                   |    |

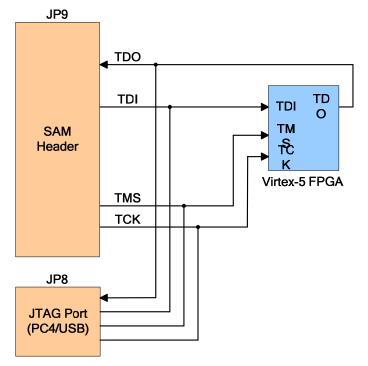

| Figure 18 - JTAG Chain on the Virtex-5 PCI Express Board                      |    |

| Figure 19 - Flash Connections for Fallback Reconfiguration                    | 37 |

| Figure 20 - SAM Interface (50-pin header)                                     | 37 |

| Figure 21 - Main Power Supply                                                 |    |

| Figure 22 - GTP Voltage Regulators                                            |    |

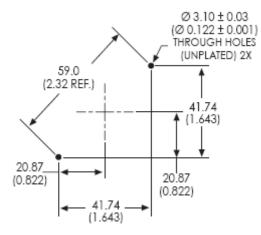

| Figure 23 - Heat Sink Mounting-Hole Pattern                                   |    |

| Figure 24 - EXP I/O Voltage Settings                                          |    |

| Figure 25 - Board Jumpers/Headers/etc                                         |    |

| Figure 26 - Configuration Mode Jumper                                         | 48 |

| Figure 27 - VIO1 SE "JP16"                                                    |    |

| Figure 28 – VIO2 SE "JP18"                                                    |    |

| Figure 29 - VIO1 DP "JP19"                                                    |    |

| Figure 30 – VIO2 DP "JP20"                                                    | 50 |

## **Tables**

| Table 1 - Ordering Information                                   | 6  |

|------------------------------------------------------------------|----|

| Table 2 - Differences between Virtex-5 devices                   | 8  |

| Table 3 - Communications Standards Supported by the Virtex-5 GTP | 8  |

| Table 4 - GTP Placement Names                                    |    |

| Table 5 - GTP Pin Assignments for PCI Express                    | 12 |

| Table 6 - GTP Pin Assignments for the SFP Interfaces             |    |

| Table 7 - SFP Host Connector Pin Description                     |    |

| Table 8 - FPGA I/O Assignments for the SFP Interfaces            | 15 |

| Table 9 - MGT Pin Assignments for Serial ATA                     |    |

| Table 10 - MGT Pin Assignments for SMA Connectors                |    |

| Table 11 - GTP Pin Assignments for 10Gbps Media Connector        |    |

| Table 12 - DDR2 SDRAM Timing Parameters                          | 18 |

| Table 13 - FPGA Pin Assignments for DDR2 SDRAM                   | 19 |

| Table 14 - DDR2 SODIMM Parameters                                |    |

| Table 15 - FPGA Pin Assignments for DDR2 SODIMM                  | 21 |

| Table 16 - Flash Interface Pin Assignments                       | 22 |

| Table 17 - On-Board Clock Sources                                | 24 |

| Table 18 - Clock Socket "U23" Pin-out                            |    |

| Table 19 - User Clock Inputs                                     |    |

| Table 20 - ICS8442 Clock Synthesizer Pin Description             | 26 |

| Table 21 - ICS8442 N Settings                                    | 26 |

| Table 22 - Examples of the ICS8442 M and N Settings              | 26 |

| Table 23 - DIP Switch Setting for M[8:0]                         | 28 |

| Table 24 - DIP Switch Setting for N[1:0]                         |    |

| Table 25 - Synthesizer Clock Outputs for M and N Values          | 29 |

| Table 26 - ICS8442 Pin Assignments                               | 30 |

| Table 27 - Ethernet PHY Hardware Strapping Options               | 31 |

| Table 28 – Faceplate Ethernet PHY "U25" Pin Assignments          | 32 |

| Table 29 - Auxiliary Ethernet PHY "U12" Pin Assignments          | 32 |

| Table 30 - USB Interface FPGA Pin-out                            | 33 |

| Table 31 - RS232 Signals                                         | 34 |

| Table 32 - RS232 Port Jumper Settings                            | 34 |

| Table 33 - Push Button Pin Assignments                           | 34 |

| Table 34 - DIP Switch Pin Assignments                            | 35 |

| Table 35 - LED Pin Assignments                                   |    |

| Table 36 – Setting the Configuration Mode "JP1"                  | 35 |

| Table 37 - Flying Lead JTAG Header                               | 36 |

| Table 38 - SAM Interface Signals                                 | 38 |

| Table 39 – I/O Bank Voltages                                     | 39 |

| Table 40 - Typical Current Measurements per MGT Tile             | 41 |

| Table 41 - Recommended Active Heat Sinks                         | 42 |

| Table 42 - EXP Connector Signals                                 | 43 |

| Table 43 - EXP v1.3 Alternate Function Pins                      | 43 |

| Table 44 - EXP Connector "JX1" Pin-out                           |    |

| Table 45 - EXP Connector "JX2" Pin-out                           | 45 |

|                                                                  |    |

## 1.0 Introduction

The purpose of this manual is to describe the functionality and contents of the Virtex-5 LXT/SXT PCI Express Development Kit from Avnet Electronics Marketing. This document includes instructions for operating the board, descriptions of the hardware features and explanations of the test code programmed in the on-board PROM. For reference design documentation, see the PDF file included with the project files of the design.

#### 1.1 Description

The Virtex-5 LXT/SXT PCI Express Development Kit provides a complete hardware environment for designers to accelerate their time to market. The kit delivers a stable platform to develop and test designs targeted to the advanced Xilinx FPGA family. The installed Virtex-5 LXT/SXT device offers a prototyping environment to effectively demonstrate the enhanced benefits of leading edge Xilinx FPGA solutions. Reference designs are included with the kit to exercise standard peripherals on the evaluation board for a quick start to device familiarization.

#### 1.2 Board Features

#### FPGA

- Xilinx Virtex-5 XC5VLX50T-FF1136 FPGA or

- Xilinx Virtex-5 XC5VLX110T-FF1136 FPGA or

- Xilinx Virtex-5 XC5VSX50T-FF1136 FPGA or

- Xilinx Virtex-5 XC5VSX95T-FF1136 FPGA

#### I/O Connectors

- Two EXP<sup>™</sup> general-purpose I/O expansion connectors

- One 50-pin 0.1" Header supports Avnet SystemACE Module (SAM)

#### RocketIO<sup>™</sup> GTP Transceiver Connectors

- Two Small-Form Pluggable (SFP) cages

- One transceiver supplied on an EXP connector for use by an expansion module

- One Serial ATA signal interface

- One CX4 connector supports 4 lanes @ 3.125 Gbps (only available on LX110T/SX95T boards)

- One PCI Express add-in card interface (8 lanes @ 2.5 Gbps)

#### Memory

- 64 MB DDR2 SDRAM components

- 256 MB DDR2 SODIMM module (only available on LX110T/SX95T boards)

- 16 MB FLASH

#### Communication

- RS-232 serial port

- USB 2.0

- Two 10/100/1000 Ethernet ports

#### Power

- Regulated 3.3V, 2.5V, and 1.2V supply voltages derived from the PCI Express slot or an external 5V supply

- SSTL2 Termination Regulators

- Point of Load Regulators for MGT supply rails

#### Configuration

- Parallel Flash interface support BPI mode of configuration

- Xilinx Parallel Cable IV or Platform USB Cable support for JTAG Programming/Configuration

- Fly-wire support for Xilinx Parallel Cable III

#### 1.3 Test Files

The Flash on the Virtex-5 LXT/SXT PCI Express Board comes programmed with a PCI Express example design. Additional test files that can be used to verify the functionality of the peripherals on the board can be found on the Avnet Electronics Marketing Design Resource Center (DRC) web site: <u>www.em.avnet.com/drc</u>. The test designs listed below are discussed in Section 3.0.

- PCI Express PIO Example

- Factory Test

- Ethernet Test

## 1.4 Reference Designs

Reference designs that demonstrate some of the potential applications of the Virtex-5 LXT/SXT PCI Express development board can be downloaded from the Avnet Design Resource Center (<u>www.em.avnet.com/drc</u>). The reference designs include all of the source code and project files necessary to implement the designs. See the PDF document included with each reference design for a complete description of the design and detailed instructions for running a demonstration on the development board. Check the DRC periodically for updates and new designs.

Figure 1 - Virtex-5 LXT/SXT PCI Express Board Picture

## 1.5 Ordering Information

The following table lists the evaluation kit part numbers and available software options. Internet link at <u>http://www.em.avnet.com/drc</u>

| Part Number             | Hardware                                                                              |

|-------------------------|---------------------------------------------------------------------------------------|

| AES-XLX-V5LXT-PCIE50-G  | Xilinx Virtex-5 PCI Express Kit populated with an XC5VLX50T<br>-1 speed grade device  |

| AES-XLX-V5LXT-PCIE110-G | Xilinx Virtex-5 PCI Express Kit populated with an XC5VLX110T<br>-2 speed grade device |

| AES-XLX-V5SXT-PCIE50-G  | Xilinx Virtex-5 PCI Express Kit populated with an XC5VSX50T<br>-1 speed grade device  |

| AES-XLX-V5SXT-PCIE95-G  | Xilinx Virtex-5 PCI Express Kit populated with an XC5VSX95T<br>-2 speed grade device  |

Table 1 - Ordering Information

Copyright © 2007 Avnet, Inc. AVNET and the AV logo are registered trademarks of Avnet, Inc. All other brands are property of their respective owners.

# 2.0 Functional Description

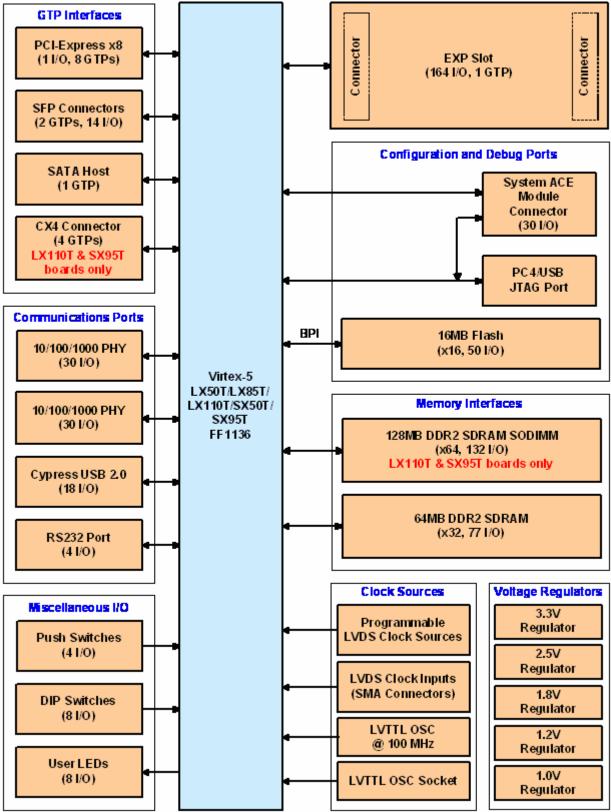

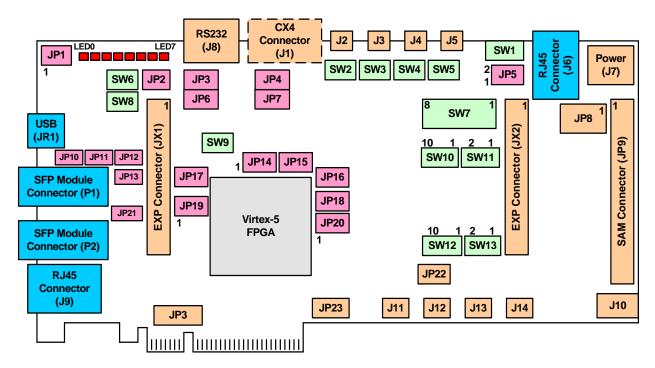

A high-level block diagram of the Virtex-5 LXT/SXT PCI Express board is shown below followed by a brief description of each subsection.

Figure 2 - Virtex-5 LXT/SXT PCI Express Board Block Diagram

#### 2.1 Xilinx Virtex-5 LXT/SXT FPGA

The Virtex-5 LXT/SXT FPGA devices available in the FF1136 package have four embedded Ethernet MAC Blocks, one embedded PCI Express Endpoint Block and six Clock Management Tiles (each tile contains two DCMs and one PLL). The following table shows the differences between these devices.

| Device     | Number of | BlockRAM | DSP48E | GTP          | I/O Pins |

|------------|-----------|----------|--------|--------------|----------|

|            | Slices    | (Kb)     | Slices | Transceivers |          |

| XC5VLX50T  | 7,200     | 2,160    | 48     | 12           | 480      |

| XC5VSX50T  | 8,160     | 4,752    | 288    | 12           | 480      |

| XC5VLX110T | 17,280    | 5,328    | 64     | 16           | 640      |

| XC5VSX95T  | 14,720    | 8,784    | 640    | 16           | 640      |

A common Printed Circuit Board (PCB) is used for all of the FPGA devices. The board was designed to primarily use the I/O pins and transceivers that are common among all of the devices in the FF1136 package. The extra I/O pins available only in the larger devices were used to implement the memory module interface (DDR2 SODIMM). Likewise the extra four transceivers available with the larger devices were used to implement the 10 Gb/s Media Connector interface. Since the smaller devices do not support these extra interfaces, they are not populated on the board.

The Virtex-5 LXT/SXT PCI Express development board uses production silicon devices. The pin-out used for the PCI Express interface supports the Xilinx recommended pin-out for production silicon.

#### 2.2 GTP Interface

The RocketIO<sup>™</sup> GTP Transceiver is a full-duplex serial transceiver for point-to-point transmission applications. Up to 24 transceivers are available on a single Virtex-5 LXT/SXT FPGA, depending on the part being used. The transceiver block is designed to operate at any serial bit rate in the range of 100 Mb/s to 3.75 Gb/s per channel, including the specific bit rates used by the communications standards listed in the following table. Multiple channels can be bonded together for increased data throughput. The data width of the FPGA fabric interface is programmable (one or two bytes) allowing the parallel data frequency to be tailored to the user application.

| Standards                | Channels (# of<br>transceivers) | I/O Bit Rate (Gb/s) |

|--------------------------|---------------------------------|---------------------|

| PCI Express              | 1, 2, 4, 8                      | 2.5                 |

| SFI-5                    | 1                               | 2.488 - 3.125       |

| OC-12                    | 1                               | 0.622               |

| OC-48                    | 1                               | 2.488               |

| Fibre Channel            | 1                               | 1.06                |

|                          |                                 | 2.12                |

| Gigabit Ethernet         | 1                               | 1.25                |

| XAUI (10-Gbit Ethernet)  | 4                               | 3.125               |

| 10-Gbit Fibre Channel    | 4                               | 3.1875              |

| Infiniband               | 1, 4                            | 2.5                 |

| HD-SDI                   | 1                               | 1.485               |

|                          |                                 | 1.4835              |

| Serial ATA               | 1                               | 1.5                 |

|                          |                                 | 3.0                 |

| Serial Rapid I/O         | 1, 4                            | 1.25                |

|                          |                                 | 2.5                 |

|                          |                                 | 3.125               |

| Aurora (Xilinx protocol) | 1, 2, 3, 4,                     | 0.100 – 3.75        |

Table 3 - Communications Standards Supported by the Virtex-5 GTP

The Virtex-5 LXT/SXT transceivers are grouped into tiles with two transceivers per tile. The two transceivers in each tile share a single PLL and other resources involving the reset and power control. A trailing number '0' or '1' is used to distinguish between the two transceivers in the tile. These transceiver tiles are physically located into a single column on the die. Each tile has a placement name associated to its X-Y coordinate on the die. For example, GTP\_Dual\_X0Y0 is the first tile in the column. The GTP\_Dual placement name is used in the User Constraint File (UCF) to map specific tiles on the device to those instantiated in a HDL design. The placement name is different for the devices that support 12 transceivers and the larger devices that support 16 as shown in the following table.

| GTP Interface | Lanes | GTP_Dual      |               | Number |

|---------------|-------|---------------|---------------|--------|

|               |       | LX50T/SX50T   | LX110T/SX95T  |        |

| 10Gb/s Media  | 0,1   | N/A           | GTP_Dual_X0Y7 | MGT124 |

| Connector     | 2,3   |               | GTP_Dual_X0Y0 | MGT126 |

| SFP           | 0,1   | GTP_Dual_X0Y5 | GTP_Dual_X0Y6 | MGT120 |

| Serial ATA    | -     | GTP_Dual_X0Y4 | GTP_Dual_X0Y5 | MGT116 |

| EXP           | -     |               |               |        |

| PCI Express   | 0,1   | GTP_Dual_X0Y3 | GTP_Dual_X0Y4 | MGT112 |

|               | 2,3   | GTP_Dual_X0Y2 | GTP_Dual_X0Y3 | MGT114 |

|               | 4,5   | GTP_Dual_X0Y1 | GTP_Dual_X0Y2 | MGT118 |

|               | 6,7   | GTP_Dual_X0Y0 | GTP_Dual_X0Y1 | MGT122 |

**Table 4 - GTP Placement Names**

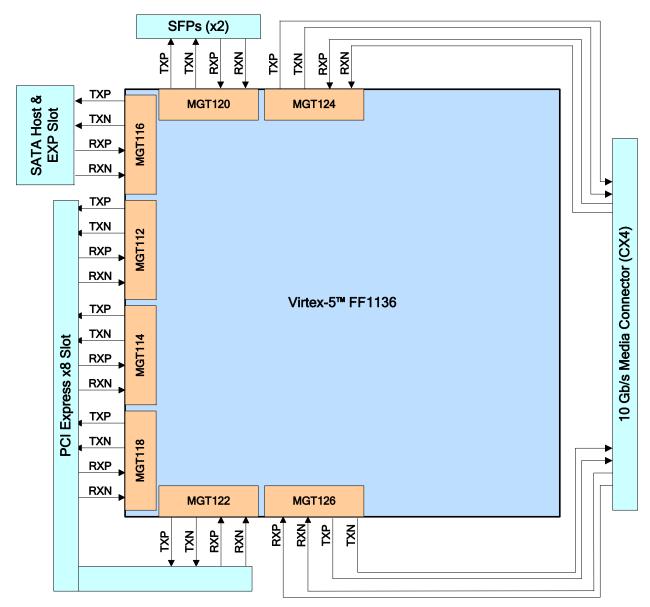

The following figure shows the 16 RocketIO transceiver ports used on the Virtex-5 LXT/SXT PCI Express board. Print this page and then rotate it right by 90 degrees to see the orientation of the part on the board. The GTP tiles are depicted in their actual locations (rough, not exact).

#### 2.2.1 GTP Reference Clock Inputs

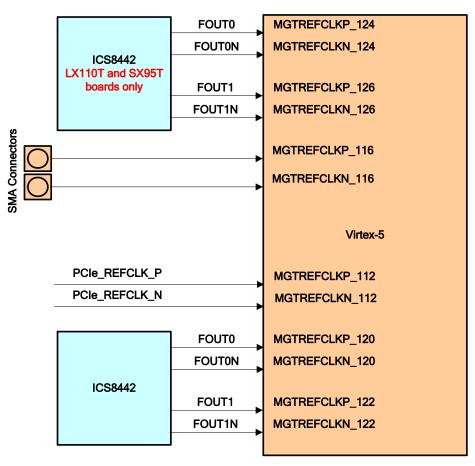

Each GTP\_Dual tile has a reference clock input that can also be used by adjacent tiles up to 3 tiles away. Several of these reference clock inputs are supplied by on-board clock sources while others are supplied externally. Two programmable LVDS synthesizers are used to provide variable clock sources to the dedicated GTP clock inputs. These synthesizers provide reference clock frequencies that support the full range of line rates. A dedicated pair of differential SMA connectors is connected to one of the GTP clock inputs. The SMA connector inputs are for user clocks generated by external test equipment or by the Virtex-5 itself on one of the SMA output connectors (requires SMA cables to make the connection). PCI Express applications use the 100MHz reference clock provided over the card edge. The following figure shows the clock sources provided to the dedicated GTP clock inputs.

Figure 4 - GTP Clock Sources on the Virtex-5 PCI Express Board

Two sets of differential SMA connectors are connected to regular I/O pins on the Virtex-5 FPGA. These SMA connectors can be used to forward a reference clock out to a scope to provide a trigger input during GTP testing.

## 2.2.2 PCI Express x8 Add-in Card

Eight of the GTP transceivers are connected to the PCI Express card edge interface. PCI Express is an enhancement to the PCI architecture where the parallel bus has been replaced with a scalable, fully serial interface. The differences in the electrical interface are transparent to the software so existing PCI software implementations are compatible. Use of the Virtex-5 LXT/SXT PCI Express board in a PCI Express application requires the implementation of the PCI Express protocol in the FPGA. The PCI Express Endpoint Block embedded in the Virtex-5 FPGA implements the PCI Express protocol and the physical layer interface to the GTP ports. This block must be instantiated in the user design. For more information, see the "Virtex-5 Endpoint Block for PCI Express Designs User Guide" on the Xilinx web site.

http://direct.xilinx.com/bvdocs/userguides/ug197.pdf.

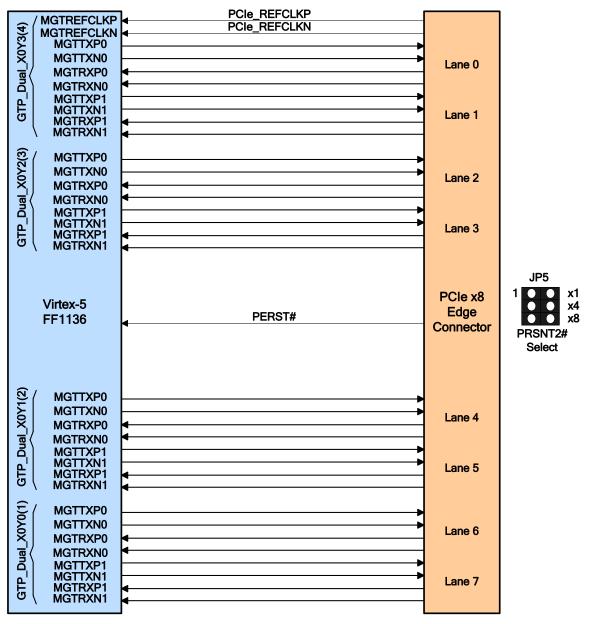

The PCI Express electrical interface on the Virtex-5 LXT/SXT PCI Express board consists of 8 lanes, each lane having a unidirectional transmit and receive differential pair. Each lane supports the first generation data rate of 2.5 Gbps. In addition to the 8 serial lanes there is a 100MHz reference clock. In order to work in open systems, add-in cards must use the 100MHz reference clock provided over the PCI Express card edge to be frequency locked with the host system. There is also a side band signal from the PCI Express card edge that connects to a regular I/O pin on the Virtex-5 FPGA. The "PERST#" signal is an active low reset signal provided by the host PCI Express slot. The following figure shows the PCI Express interface to the Virtex-5 FPGA.

The lane width of the PCI Express interface is determined by the PRSNT1# and PRSNT2# connections. There are separate PRSNT2# pins for each of the lane options: one lane (x1), four lanes (x4) and eight lanes (X8). These pins are pulled-up on the host motherboard. There is a single PRSNT1# pin that is pulled-low or tied to GND on the host motherboard. The add-in card connects the PRSNT1# pin to the PRSNT2# pin for the widest lane option in most applications, which effectively pulls the corresponding PRSNT2# pin low. This indicates to the host controller the lane width supported by the add-in card. The Virtex-5 LXT/SXT PCI Express board provides the ability for the user to select the lane width by connecting the desired PRSNT2# pin with a jumper on JP5. See Appendix A for more information about the JP5 jumper settings.

The PCI Express transmit lanes are AC coupled (DC blocking capacitors are included in the signal path) on the development board as required by the PCI Express specification. The Virtex-5 LXT/SXT PCI Express board takes advantage of the polarity inversion feature of the GTP transceivers. The "P" and "N" of all of the odd-numbered PCI Express lanes are swapped on the board to improve the PCB routing. Each GTP has attributes that are used to enable polarity inversion on either the transmit or receive pairs, or both. The polarity inversion attributes are "TXPOLARITY" for the transmit pairs and "RXPOLARITY" for the receive pairs. Setting these attributes to a logic 1 enables the inversion.

| GTP Instance  | Net Name               | Connector.pin# | Virtex-5 pin# | P/N Swapped? |

|---------------|------------------------|----------------|---------------|--------------|

| LX50T/SX50T:  | PCIe_RX0P              | P4.B14         | N1            | No           |

| GTP_Dual_X0Y3 | PCIe_RX0N              | P4.B15         | P1            |              |

| LX110T/SX95T: | PCIe_TX0P              | P4.A16         | M2            | No           |

| GTP_Dual_X0Y4 | PCIe_TX0N              | P4.A17         | N2            |              |

|               |                        |                |               |              |

|               | PCIe_RX1P              | P4.B19         | R1            | Yes (RX)     |

|               | PCIe_RX1N              | P4.B20         | T1            |              |

|               | PCIe_TX1P              | P4.A21         | T2            | Yes (TX)     |

|               | PCIe_TX1N              | P4.A22         | U2            |              |

|               |                        |                |               |              |

| LX50T/SX50T:  | PCIe_RX2P              | P4.B23         | W1            | No           |

| GTP_Dual_X0Y2 | PCIe_RX2N              | P4.B24         | Y1            |              |

| LX110T/SX95T: | PCIe_TX2P              | P4.A25         | V2            | No           |

| GTP_Dual_X0Y3 | PCIe_TX2N              | P4.A26         | W2            |              |

|               |                        |                |               |              |

|               | PCIe_RX3P              | P4.B27         | AA1           | Yes (RX)     |

|               | PCIe_RX3N              | P4.B28         | AB1           |              |

|               | PCIe_TX3P              | P4.A29         | AB2           | Yes (TX)     |

|               | PCIe_TX3N              | P4.A30         | AC2           |              |

| LX50T/SX50T:  | PCIe_RX4P              | P4.B33         | AE1           | No           |

| GTP_Dual_X0Y1 | PCIe_RX4N              | P4.B33         | AF1           | INU          |

| LX110T/SX95T: | PCIe_TX4P              | P4.B34         | APT<br>AD2    | No           |

| GTP_Dual_X0Y2 | PCIe_TX4P<br>PCIe_TX4N | P4.A35         | AD2<br>AE2    | INO          |

|               | PCIE_174IN             | F4.A30         | AEZ           |              |

|               | PCIe_RX5P              | P4.B37         | AG1           | Yes (RX)     |

|               | PCIe_RX5N              | P4.B38         | AH1           |              |

|               | PCIe_TX5P              | P4.A39         | AH2           | Yes (TX)     |

|               | PCIe_TX5N              | P4.A40         | AJ2           | ( )          |

|               |                        |                |               |              |

| LX50T/SX50T:  | PCIe_RX6P              | P4.B41         | AL1           | No           |

| GTP_Dual_X0Y0 | PCIe_RX6N              | P4.B42         | AM1           |              |

| LX110T/SX95T: | PCIe_TX6P              | P4.A43         | AK2           | No           |

| GTP_Dual_X0Y1 | PCIe_TX6N              | P4.A44         | AL2           |              |

|               |                        |                |               |              |

|               | PCIe_RX7P              | P4.B45         | AP2           | Yes (RX)     |

|               | PCIe_RX7N              | P4.B46         | AP3           |              |

|               | PCIe_TX7P              | P4.A47         | AN3           | Yes (TX)     |

|               | PCIe_TX7N              | P4.A48         | AN4           |              |

Table 5 - GTP Pin Assignments for PCI Express

#### 2.2.3 SFP Connectors

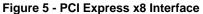

Two MGT transceivers are connected to Small Form-factor Pluggable (SFP) interfaces, which provide the ability to support optical links with the addition of optical transceiver modules (not included in the kit). The following figure shows a high-level block diagram of the SFP interfaces on the development board. This interface utilizes one GTP\_Dual tile and a set of low-speed control signals to interface to two SFP modules. One of the programmable LVDS synthesizers on the board is used to provide the reference clock. The SFP interfaces on the Virtex-5 LXT/SXT PCI Express board have been designed to support transceivers with transmission rates up to 3.75Gbps operating over multimode or single mode fiber.

Figure 6 - SFP Module Interfaces

The SFP connectors include a Host Board Connector, and top and bottom EMI cages. The Host Connectors are directly connected or DC coupled to the GTP ports. SFP compliant modules include AC coupling capacitors in the modules for both the transmit and receive signal paths so the AC coupling internal to the Virtex-5 LXT/SXT GTP receiver may be bypassed (RXDCCOUPLE = TRUE). The "P" and "N" of the transmit differential pair is swapped on the board for the SFP0 interface to improve the PCB routing. Set the "TXPOLARITY0" attribute to logic 1 to enable the polarity inversion feature for the transceiver connected to the SFP0 interface. Likewise the receive differential pair is swapped on the board for SFP1. Set the "RXPOLARITY1" attribute to logic 1 to enable polarity inversion for the SFP1 transceiver. MGT120 transceivers 0 and 1 are connected to the two SFP host connectors labeled "P1" and "P2" as indicated in the previous figure. The MGT120 tile is GTP\_Dual "X0Y5" in the LX50T/SX50T devices or GTP\_Dual "X0Y6" in the LX110T/SX95T devices.

| GTP Instance  | Net Name | Connector.pin# | Virtex-5 pin# | P/N Swapped? |

|---------------|----------|----------------|---------------|--------------|

| LX50T/SX50T:  | SFP0_RXN | P1.12          | A2            | No           |

| GTP_Dual_X0Y5 | SFP0_RXP | P1.13          | A3            |              |

| LX110T/SX95T: | SFP0_TXP | P1.18          | B3            | Yes (TX)     |

| GTP_Dual_X0Y6 | SFP0_TXN | P1.19          | B4            |              |

|               |          |                |               |              |

|               | SFP1_RXN | P2.12          | D1            | Yes (RX)     |

|               | SFP1_RXP | P2.13          | C1            |              |

|               | SFP1_TXP | P2.18          | E2            | No           |

|               | SFP1_TXN | P2.19          | D2            |              |

Table 6 - GTP Pin Assignments for the SFP Interfaces

SFP modules connect to the board via the Host Board Connector defined in the SFP Multi-Source Agreement (MSA). This 20pin connector provides connections for power, ground, high-speed serial data, and the low-speed control signals for controlling the operation of the SFP module. The following figure shows the host connector used on the Virtex-5 LXT/SXT PCI Express board.

Figure 7 - Host Board Connector AMP 1367073-1 (photo taken from AMP Web Page)

The following table lists the Host Board Connector pin assignments and provides a brief description of each signal.

| Pin Number | Name        | Function                                                 |  |

|------------|-------------|----------------------------------------------------------|--|

| 1          | VEET        | Transmitter Ground                                       |  |

| 2          | Tx Fault    | Transmitter Fault Indication                             |  |

| 3          | Tx Disable  | Transmitter Disable                                      |  |

| 4          | MOD-DEF(2)  | Module Definition 2 (Serial Interface Data Line)         |  |

| 5          | MOD-DEF(1)  | Module Definition 1 (Serial Interface Clock Line)        |  |

| 6          | MOD-DEF(0)  | Module Definition 0 (Module Present Signals, active low) |  |

| 7          | Rate Select | Not Connected                                            |  |

| 8          | LOS         | Loss of Signal                                           |  |

| 9          | VEER        | Receiver Ground                                          |  |

| 10         | VEER        | Receiver Ground                                          |  |

| 11         | VEER        | Receiver Ground                                          |  |

| 12         | RD-         | Inverse Received Data Out                                |  |

| 13         | RD+         | Received Data Out                                        |  |

| 14         | VEER        | Receiver Ground                                          |  |

| 15         | VCCR        | Receiver Power                                           |  |

| 16         | VCCT        | Transmitter Power                                        |  |

| 17         | VEET        | Transmitter Ground                                       |  |

| 18         | TD+         | Transmitter Data In                                      |  |

| 19         | TD-         | Inverse Transmitter Data In                              |  |

| 20         | VEET        | Transmitter Ground                                       |  |

Table 7 - SFP Host Connector Pin Description

The following table lists the FPGA I/O assignments for the SFP interfaces.

| Net Name        | Virtex-5 Pin# |  |  |  |  |

|-----------------|---------------|--|--|--|--|

| SFP #0          |               |  |  |  |  |

| SFP0_LOS        | H29           |  |  |  |  |

| SFP0_MOD0       | E29           |  |  |  |  |

| SFP0_MOD1       | F30           |  |  |  |  |

| SFP0_MOD2       | G30           |  |  |  |  |

| SFP0_RSEL       | F29           |  |  |  |  |

| SFP0_TX_DISABLE | E31           |  |  |  |  |

| SFP0_TX_FAULT   | F31           |  |  |  |  |

| SFP #1          | SFP #1        |  |  |  |  |

| SFP1_LOS        | H27           |  |  |  |  |

| SFP1_MOD0       | E26           |  |  |  |  |

| SFP1_MOD1       | G28           |  |  |  |  |

| SFP1_MOD2       | E27           |  |  |  |  |

| SFP1_RSEL       | H28           |  |  |  |  |

| SFP1_TX_DISABLE | F28           |  |  |  |  |

| SFP1_TX_FAULT   | E28           |  |  |  |  |

#### Table 8 - FPGA I/O Assignments for the SFP Interfaces

#### 2.2.4 Serial ATA Connector

One GTP transceiver is connected to a Serial ATA host connector that can be used to connect an I/O device such as a hard drive to the board. Only the signal connector is present on the Virtex-5 LXT/SXT PCI Express board. Power for the Serial ATA peripheral must be supplied externally. MGT116 transceiver #0 is connected to the vertical cable-to-board connector labeled "P3". The connector is keyed to ensure the correct polarity. The MGT116 tile is GTP\_Dual "X0Y4" in the LX50T/SX50T devices or GTP\_Dual "X0Y5" in the LX110T/SX95T devices.

| GTP Instance  | Net Name | Connector.pin# | Virtex-5 pin# | P/N Swapped? |

|---------------|----------|----------------|---------------|--------------|

| LX50T/SX50T:  | SATA_TXP | P3.2           | F2            | No           |

| GTP_Dual_X0Y5 | SATA_TXN | P3.3           | G2            |              |

| LX110T/SX95T: | SATA_RXN | P3.5           | H1            | No           |

| GTP_Dual_X0Y6 | SATA_RXP | P3.6           | G1            |              |

#### 2.2.5 GTP on EXP Connector JX1

One GTP transceiver is brought out to the board-to-board connector labeled "JX1" on the board for use by EXP daughter cards. The MGT116 transceiver #1 is directly connected to JX1 pins 54 and 56 (RX+ and RX-) and pins 53 and 55 (TX+ and TX-). The user must evaluate whether AC coupling is required on the daughter card to safely interface with the Virtex-5 GTP transceiver. The MGT116 tile is GTP\_Dual "X0Y4" in the LX50T/SX50T devices or GTP\_Dual "X0Y5" in the LX110T/SX95T devices.

| GTP Instance  | Net Name | Connector.pin# | Virtex-5 pin# | P/N Swapped? |

|---------------|----------|----------------|---------------|--------------|

| LX50T/SX50T:  | EXP_TXP  | JX1.53         | L2            | No           |

| GTP_Dual_X0Y5 | EXP_TXN  | JX1.55         | K2            |              |

| LX110T/SX95T: | EXP_RXP  | JX1.54         | K1            | No           |

| GTP_Dual_X0Y6 | EXP_RXN  | JX1.56         | J1            |              |

Table 10 - MGT Pin Assignments for SMA Connectors

#### 2.2.6 10 Gb/s Media Connector

Four GTP transceivers are connected to a board-to-cable connector for general purpose use. The connector footprint on the Virtex-5 LXT/SXT PCI Express board supports the jack screw attachment version of the Molex LaneLink<sup>™</sup> 4X I/O connector. This surface-mount connector is optimized for high-speed differential signals supporting serial data rates up to 3.125 Gb/s. This interface can be used for short-range, point-to-point applications requiring full-duplex operation over four lanes (8 unidirectional signals: 4 transmit pairs and 4 receive pairs). This interface utilizes two GTP tiles to support four RocketIO transceivers running at 3.125 Gb/s to implement a 10 Gb/s channel. A single cable can be used to connect to EXP daughter cards with 10 Gb/s capable PHY devices for prototyping purposes. The cable is not included in the kit but can be purchased from an authorized Molex distributor (P/N: 74506-3001). The LaneLink 4X connector is labeled "J1" on the board. The following figure shows a high-level block diagram of the 10 Gb/s interface on the development board.

| GTP_Dual_X0Y7 | MGTRXP/N0<br>MGTRXP/N1<br>MGTTXP/N0<br>MGTTXP/N1 | RX1_P/N<br>RX0_P/N<br>TX1_P/N<br>TX0_P/N |                               |

|---------------|--------------------------------------------------|------------------------------------------|-------------------------------|

|               | Virtex-5<br>X110T/SX95T<br>Only                  | RX3_P/N                                  | 10 Gb/s<br>Media<br>Connector |

| GTP_Dual_X0Y0 | MGTRXP/N0<br>MGTRXP/N1<br>MGTTXP/N0              | RX2_P/N<br>TX3_P/N                       |                               |

| GTP           | MGTTXP/N1                                        | TX2_P/N                                  |                               |

Figure 8 - 10 Gb/s Media Connector Interface

The 10 Gb/s Media Connector is directly connected or DC coupled to the GTP ports. Care must be taken not to exceed the GTP receiver tolerances when interfacing to external devices. The AC coupling internal to the Virtex-5 LXT/SXT MGT receiver should not be bypassed unless the external connection has DC blocking capacitors on the transmit lanes. The "P" and "N" of some of the differential pairs are swapped on the board to improve the PCB routing to the 10 Gb/s Media Connector. Set the "RXPOLARITYx" and "TXPOLARITYx" attributes to logic 1 to enable the polarity inversion feature for the transceivers indicated in the following table (see the "P/N Swapped" column). This interface utilizes four of the GTP ports; MGT124 transceivers 0 and 1, and MGT126 transceivers 0 and 1. The programmable LVDS clock synthesizer labeled "U17" on the board is used to provide the reference clock to both tiles.

| GTP Instance  | Net Name | Connector.pin# | Virtex-5 pin# | P/N Swapped? |

|---------------|----------|----------------|---------------|--------------|

| LX110T/SX95T: | CX4_RX0P | J1.2           | A6            | No           |

| GTP_Dual_X0Y7 | CX4_RX0N | J1.3           | A7            |              |

|               | CX4_TX0N | J1.23          | B6            | No           |

|               | CX4_TX0P | J1.24          | B5            |              |

|               |          |                |               |              |

|               | CX4_RX1P | J1.5           | A8            | Yes (RX)     |

|               | CX4_RX1N | J1.6           | A9            |              |

|               | CX4_TX1N | J1.20          | B10           | Yes (TX)     |

|               | CX4_TX1P | J1.21          | B9            |              |

|               |          |                |               |              |

| LX110T/SX95T: | CX4_RX2P | J1.8           | AP9           | No           |

| GTP_Dual_X0Y0 | CX4_RX2N | J1.9           | AP8           |              |

|               | CX4_TX2N | J1.17          | AN10          | Yes (TX)     |

|               | CX4_TX2P | J1.18          | AN9           |              |

|               |          |                |               |              |

|               | CX4_RX3P | J1.11          | AP6           | No           |

|               | CX4_RX3N | J1.12          | AP7           |              |

|               | CX4_TX3N | J1.14          | AN6           | No           |

|               | CX4_TX3P | J1.15          | AN5           |              |

Table 11 - GTP Pin Assignments for 10Gbps Media Connector

#### 2.3 Memory

The Virtex-5 LXT/SXT PCI Express development board is populated with both high-speed RAM and non-volatile ROM to support various types of applications. The boards with the LX50T/SX50T devices have 64 Megabytes (MB) of DDR2 SDRAM and 16 MB of Flash. The boards with the LX110T/SX95T devices also have 64MB of DDR2 SDRAM but have a larger density Flash device (32MB) and an additional 256MB memory module. The memory module interface is only available with the larger FPGAs that have the extra four I/O banks. The I/O pins used for the module interface are no-connects in the smaller devices. If additional memory is necessary for development, check the Avnet Design Resource Center (DRC) for the availability of EXP compliant daughter cards with expansion memory (sold separately). Here is the link to the DRC web page: www.em.avnet.com/drc.

## 2.3.1 DDR2 SDRAM Interface

Two Micron DDR2 SDRAM devices, part number MT47H16M16BG-5E, make up the 32-bit data bus. Each device provides 32MB of memory on a single IC and is organized as 4 Megabits x 16 x 4 banks (256 Megabit). The Virtex-5 LXT/SXT PCI Express Board can support larger devices with addressing support for up to 128MB (two 512-Megabit devices). The device has an operating voltage of 1.8V and the interface is JEDEC Standard SSTL\_18 (Class I for unidirectional signals, Class II for bidirectional signals). The -5 speed grade supports 5 ns cycle times with a 3 clock read latency (DDR2-400). The following figure shows a high-level block diagram of the DDR2 SDRAM interface on the development board.

Figure 9 - DDR2 SDRAM Interface

The DDR2 signals are connected to I/O Banks 17 and 21 of the Virtex-5 LXT/SXT FPGA. The output supply pins (VCCO) for Banks 17 and 21 are connected to 1.8 Volts. This supply rail can be measured at test point TP6, which can be found in the area between the power modules and the SAM header labeled "JP9". The reference voltage pins (VREF) for Banks 17 and 21 are connected to the reference output of the National LP2997 DDR2 Termination Linear Regulator. This rail provides the voltage reference necessary for the SSTL\_18 I/O standard. The LP2997 regulator also provides the termination supply rail. The termination voltage is 0.9 Volts and can be measured at test point TP5, which can be found next to the DDR2 SDRAM device labeled "U19".

The following table provides timing and other information about the Micron device necessary to implement a DDR2 memory controller.

| MT47H16M16BG-5E: Timing Parameters            | Time (ps) or<br>Number |

|-----------------------------------------------|------------------------|

| Load Mode Register time (TMRD)                | 2 tCK                  |

| Write Recovery time (TWR)                     | 15000                  |

| Write-to-Read Command Delay (TWTR)            | 10000                  |

| Delay between ACT and PRE Commands (TRAS)     | 40000                  |

| Delay after ACT before another ACT (TRC)      | 55000                  |

| Delay after AUTOREFRESH Command (TRFC)        | 75000                  |

| Delay after ACT before READ/WRITE (TRCD)      | 15000                  |

| Delay after ACT before another row ACT (TRRD) | 10000                  |

| Delay after PRECHARGE Command (TRP)           | 15000                  |

| Refresh Command Interval (TREFC)              | 7000000                |

| Avg. Refresh Period (TREFI)                   | 7800000                |

| Memory Data Width (DWIDTH) (2 devices)        | 32                     |

| Row Address Width (AWIDTH)                    | 13                     |

| Column Address Width (COL_AWIDTH)             | 9                      |

| Bank Address Width (BANK_AWIDTH)              | 2                      |

| Memory Range (64 MB total)                    | 0x3FFFFFF              |

The following guidelines were used in the design of the DDR2 interface to the Virtex-5 LXT/SXT FPGA. These guidelines are based on Micron recommendations and board level simulation.

- 50 ohm\* controlled trace impedance

- Dedicated data bus with matched trace lengths (+/- 50 mils)

- Memory clocks and data strobes routed differentially

- Series termination on bidirectional signals at the memory device

- Parallel termination following the memory device connection on shared signals (control, address)

- 50 ohm\* pull-up resistor to the termination supply (0.9V) on clock signals

- 100 ohm\* pull-up resistor to the termination supply on each branch of shared signals (control, address)

- Termination supply that can both source and sink current

- Feedback clock routed with twice the length to simulate the total flight time

\* Ideal impedance values. Actual may vary.

Some of the design considerations were specific to the Virtex-5 architecture. For example, the data strobe signals (DQS) were placed on Clock Capable I/O pins in order to support data capture techniques utilizing the SERDES function of the Virtex-5 I/O blocks. The appropriate DDR2 memory signals were placed in the clock regions that correspond to these particular Clock Capable I/O pins.

#### The following table contains the FPGA pin numbers for the DDR2 SDRAM interface.

| Net Name        | Virtex-5 pin# | Net Name | Virtex-5 pin# |

|-----------------|---------------|----------|---------------|

| DDR2_A0         | V27           | DDR2_D0  | AF29          |

| DDR2_A1         | V28           | DDR2_D1  | AF31          |

| DDR2_A2         | W24           | DDR2_D2  | Y29           |

| DDR2_A3         | AH28          | DDR2_D3  | AJ31          |

| DDR2_A4         | Y26           | DDR2_D4  | AK31          |

| DDR2_A5         | AG28          | DDR2_D5  | Y28           |

| DDR2_A6         | W27           | DDR2_D6  | AE31          |

| DDR2_A7         | AF28          | DDR2_D7  | AC29          |

| DDR2_A8         | AA28          | DDR2_D8  | AD31          |

| DDR2_A9         | AE28          | DDR2_D9  | AH29          |

| DDR2_A10        | W29           | DDR2_D10 | AA30          |

| DDR2_A11        | Y27           | DDR2_D11 | AJ30          |

| DDR2 A12        | AE27          | DDR2 D12 | AH30          |

| —               | 1             | DDR2 D13 | AA29          |

| DDR2_BA0        | AC27          | DDR2_D14 | AG30          |

| DDR2_BA1        | AC28          | DDR2 D15 | Y31           |

|                 |               | DDR2 D16 | AE26          |

| DDR2_CS#        | W25           | DDR2 D17 | AG25          |

| DDR2 ODT        | V25           | DDR2_D18 | AJ25          |

| DDR2 WE#        | AB28          | DDR2 D20 | AA26          |

| DDR2_RAS#       | W26           | DDR2_D21 | AH25          |

| DDR2 CAS#       | V24           | DDR2 D22 | AF25          |

| DDR2 CLKEN      | AB27          | DDR2 D23 | AF26          |

| DDR2_CK0        | AE29          | DDR2_D24 | AJ27          |

| DDR2 CK0#       | AD29          | DDR2 D25 | AC25          |

| DDR2_CK1        | AD26          | DDR2_D26 | AJ26          |

| DDR2_CK1#       | AD25          | DDR2_D27 | AF24          |

|                 |               | DDR2 D28 | AE24          |

| DDR2_DQS0       | AB31          | DDR2_D29 | AK26          |

| DDR2 DQS0#      | AA31          | DDR2 D30 | AC24          |

| DDR2 DQS1       | AB30          | DDR2 D31 | AH27          |

| DDR2_DQS1#      | AC30          |          |               |

| DDR2_DQS2       | AK29          | DDR2_DM0 | AF30          |

| DDR2_DQS2#      | AJ29          | DDR2_DM1 | AD30          |

| DDR2_DQS3       | AK28          | DDR2_DM2 | AA25          |

| DDR2 DQS3#      | AK27          | DDR2 DM3 | AA24          |

|                 | 1             |          | 1             |

| DDR2_CLK_FB_OUT | AD24          |          |               |

| DDR2_CLK_FB_IN  | AG18          |          |               |

## Table 13 - FPGA Pin Assignments for DDR2 SDRAM

## 2.3.2 DDR2 SODIMM Interface (LX110T/SX95T Only)

The extra I/O pins available with the LX110T and SX95T devices are used to implement a 200-pin, small outline, dual in-line memory module (SODIMM) interface. A Micron DDR2 SDRAM module, part number MT4HTF3264HY-53ED3, is populated in the SODIMM connector labeled "U33" on the backside of the Virtex-5 LXT/SXT PCI Express board. This single rank module provides 256MB of memory organized as 32 Meg x 64. The bandwidth of the -53E speed grade module is 4.3GB/s with a memory clock of 533MHz (3.75ns). The Virtex-5 LXT/SXT PCI Express board was designed to support larger density modules with eight-bank addressing and dual rank modules with two chip selects.

The DDR2 SODIMM signals are connected to I/O Banks 5, 6, 23 and 25 of the Virtex-5 LXT/SXT FPGA. The output supply pins (VCCO) for these banks are connected to 1.8 Volts. A second National LP2997 Termination Regulator is dedicated to the SODIMM interface to provide the reference and termination voltage rails (0.9 Volts) necessary to implement the SSTL\_18 I/O standard. The termination voltage rail "0.9VTT\_DM" can be measured at test point TP3, which can be found next to the DDR2 SDRAM device labeled "U14".

The following table provides timing and other information about the Micron device necessary to implement a DDR2 SODIMM memory controller.

| MT4HTF3264HY-53ED3: Timing Parameters         | Time (ps) or<br>Number |

|-----------------------------------------------|------------------------|

| Load Mode Register time (TMRD)                | 2 tCK                  |

| Write Recovery time (TWR)                     | 15000                  |

| Write-to-Read Command Delay (TWTR)            | 10000                  |

| Delay between ACT and PRE Commands (TRAS)     | 40000                  |

| Delay after ACT before another ACT (TRC)      | 55000                  |

| Delay after AUTOREFRESH Command (TRFC)        | 75000                  |

| Delay after ACT before READ/WRITE (TRCD)      | 15000                  |

| Delay after ACT before another row ACT (TRRD) | 10000                  |

| Delay after PRECHARGE Command (TRP)           | 15000                  |

| Refresh Command Interval (TREFC)              | 7000000                |

| Avg. Refresh Period (TREFI)                   | 7800000                |

|                                               |                        |

| Memory Data Width (DWIDTH)                    | 64                     |

| Row Address Width (AWIDTH)                    | 13                     |

| Column Address Width (COL_AWIDTH)             | 10                     |

| Bank Address Width (BANK_AWIDTH)              | 2                      |

| Memory Range (256 MB total)                   | 0xFFFFFFF              |

Table 14 - DDR2 SODIMM Parameters

The following guidelines were used in the design of the DDR2 SODIMM interface to the Virtex-5 LXT/SXT FPGA. These guidelines are based on Micron recommendations and board level simulation.

- 50 ohm\* controlled trace impedance

- Dedicated data bus with matched trace lengths (+/- 50 mils)

- Memory clocks and data strobes routed differentially

- 50 ohm\* pull-up resistor to the termination supply (0.9V) on clock, control and address signals

- Termination supply that can both source and sink current

- Feedback clock routed with twice the length to simulate the total flight time

\* Ideal impedance values. Actual may vary.

Some of the design considerations were specific to the Virtex-5 architecture. For example, the data strobe signals (DQS) were placed on Clock Capable I/O pins in order to support data capture techniques utilizing the SERDES function of the Virtex-5 I/O blocks. The appropriate DDR2 memory signals were placed in the clock regions that correspond to these particular Clock Capable I/O pins.

## The following table contains the FPGA pin numbers for the DDR2 SODIMM interface.

| Net Name        | Virtex-5<br>pin# | Net Name        | Virtex-5<br>pin# | Net Name        | Virtex-5<br>pin# |

|-----------------|------------------|-----------------|------------------|-----------------|------------------|

| DDR2_DIMM_A0    | D29              | DDR2_DIMM_D0    | AJ12             | DDR2_DIMM_D32   | C22              |

| DDR2_DIMM_A1    | D26              | DDR2_DIMM_D1    | AK12             | DDR2_DIMM_D33   | A21              |

| DDR2_DIMM_A2    | D27              | DDR2_DIMM_D2    | AJ14             | DDR2_DIMM_D34   | C20              |

| DDR2_DIMM_A3    | C27              | DDR2_DIMM_D3    | AK14             | DDR2_DIMM_D35   | B20              |

| DDR2_DIMM_A4    | AL31             | DDR2_DIMM_D4    | AK13             | DDR2_DIMM_D36   | D25              |

| DDR2_DIMM_A5    | AP26             | DDR2_DIMM_D5    | AL13             | DDR2 DIMM D37   | A25              |

| DDR2_DIMM_A6    | AM31             | DDR2_DIMM_D6    | AN15             | DDR2 DIMM D38   | A24              |

| DDR2_DIMM_A7    | AP31             | DDR2_DIMM_D7    | AP15             | DDR2 DIMM D39   | C23              |

| DDR2_DIMM_A8    | AP25             | DDR2 DIMM DM0   | AL14             | DDR2 DIMM DM4   | C24              |

| DDR2 DIMM A9    | AH24             | DDR2_DIMM_DQS0  | AK16             | DDR2 DIMM DQS4  | B25              |

| DDR2_DIMM_A10   | E24              | DDR2_DIMM_DQS0# | AL16             | DDR2_DIMM_DQS4# | C25              |

| DDR2_DIMM_A11   | AL30             |                 |                  |                 |                  |

| DDR2_DIMM_A12   | AN24             | DDR2_DIMM_D8    | AL15             | DDR2 DIMM D40   | A20              |

|                 |                  | DDR2_DIMM_D9    | AM15             | DDR2_DIMM_D41   | C19              |

| DDR2_DIMM_BA0   | D24              | DDR2_DIMM_D10   | AJ17             | DDR2_DIMM_D42   | C18              |

| DDR2_DIMM_BA1   | C28              | DDR2_DIMM_D11   | AK17             | DDR2_DIMM_D43   | B18              |

| DDR2 DIMM BA2   | D31              | DDR2_DIMM_D12   | AM16             | DDR2 DIMM D44   | A23              |

|                 |                  | DDR2_DIMM_D13   | AP16             | DDR2_DIMM_D45   | B23              |

| DDR2_DIMM_S0#   | F24              | DDR2_DIMM_D14   | AN17             | DDR2_DIMM_D46   | B22              |

| DDR2_DIMM_S1#   | AP24             | DDR2 DIMM D15   | AP17             | DDR2_DIMM_D47   | B21              |

| DDR2_DIMM_ODT0  | E21              | DDR2 DIMM DM1   | AM17             | DDR2 DIMM DM5   | A19              |

| DDR2_DIMM_ODT1  | AH23             | DDR2 DIMM DQS1  | AJ16             | DDR2 DIMM DQS5  | B27              |

| DDR2 DIMM WE#   | E23              | DDR2 DIMM DQS1# | AJ15             | DDR2 DIMM DQS5# | A26              |

| DDR2_DIMM_RAS#  | C30              |                 |                  |                 |                  |

| DDR2_DIMM_CAS#  | E22              | DDR2_DIMM_D16   | AN20             | DDR2_DIMM_D48   | E18              |

| DDR2_DIMM_CKE0  | D22              | DDR2 DIMM D17   | AM20             | DDR2 DIMM D49   | F18              |

| DDR2_DIMM_CKE1  | AM30             | DDR2 DIMM D18   | AP20             | DDR2 DIMM D50   | G17              |

| DDR2_DIMM_CK0   | AN19             | DDR2 DIMM D19   | AM21             | DDR2 DIMM D51   | D17              |

| DDR2_DIMM_CK0#  | AP19             | DDR2 DIMM D20   | AM27             | DDR2_DIMM_D52   | D20              |

| DDR2_DIMM_CK1   | A30              | DDR2_DIMM_D21   | AN27             | DDR2_DIMM_D53   | F20              |

| DDR2_DIMM_CK1#  | B30              | DDR2 DIMM D22   | AM28             | DDR2 DIMM D54   | D19              |

|                 |                  | DDR2 DIMM D23   | AN28             | DDR2 DIMM D55   | E19              |

| DDR2_DIMM_SA0   | B15              | DDR2 DIMM DM2   | AP27             | DDR2 DIMM DM6   | G20              |

| DDR2_DIMM_SA1   | A15              | DDR2_DIMM_DQS2  | AN25             | DDR2_DIMM_DQS6  | E17              |

|                 |                  | DDR2 DIMM DQS2# | AM25             | DDR2 DIMM DQS6# | E16              |

| DDR2_DIMM_SDA   | D15              |                 |                  |                 |                  |

| DDR2_DIMM_SCL   | F15              | DDR2 DIMM D24   | AP21             | DDR2_DIMM_D56   | F16              |

|                 |                  | DDR2_DIMM_D25   | AP22             | DDR2_DIMM_D57   | D16              |

| DDR2 DIMM EVENT | D21              | DDR2 DIMM D26   | AM22             | DDR2 DIMM D58   | C14              |

|                 | <u> </u>         | DDR2_DIMM_D27   | AN23             | DDR2_DIMM_D59   | F14              |

| DDR2_CLK_FB_OUT | D30              | DDR2_DIMM_D28   | AL29             | DDR2 DIMM D60   | B17              |

| DDR2_CLK_FB_IN  | J16              | DDR2_DIMM_D29   | AN29             | DDR2_DIMM_D61   | C17              |

|                 |                  | DDR2_DIMM_D30   | AN30             | DDR2_DIMM_D62   | B16              |

|                 |                  | DDR2 DIMM D31   | AP30             | DDR2 DIMM D63   | A16              |

|                 |                  | DDR2_DIMM_DM3   | AN22             | DDR2 DIMM DM7   | A14              |

|                 |                  | DDR2_DIMM_DQS3  | AL25             | DDR2_DIMM_DQS7  | D14              |

|                 |                  | DDR2_DIMM_DQS3# | AL24             | DDR2_DIMM_DQS7# | E14              |

Table 15 - FPGA Pin Assignments for DDR2 SODIMM

#### 2.3.3 Flash Interface

The Flash memory consists of a single Intel StrataFlash Embedded Memory (P30) device in a 64-ball Easy BGA package. The boards with the LX50T/SX50T FPGA have a 128-Mbit Flash device while the boards with the larger LX110T/SX95T FPGA have a 256-Mbit Flash. The P30 device is an asynchronous memory that also supports a synchronous-burst read mode for high-performance applications. The P30 device has an 85 nanosecond access time. The footprint on the Virtex-5 LXT/SXT PCI Express board also supports the J3 device (28FxxxJ3A) in the same package with a jumper resistor to select the appropriate VCC voltage (1.8V for the P30 device or 3.3V for the J3 device). The jumper resistor labeled "JT2" on the board sets the supply voltage (1.8V default). The Flash interface connects to the designated pins required for BPI configuration mode. These pins are in Banks 1, 2 and 4 of the Virtex-5 FPGA. The Flash I/O voltage (VCCQ) is set to 3.3V to match the VCCO voltage of Banks 1 and 2. The following figure shows a high-level block diagram of the Flash interface on the development board.

Figure 10 - Flash Interface

The following table contains the FPGA pin numbers for the Flash interface.

| Net Name  | Virtex-5 pin# | Net Name    | Virtex-5 pin# |

|-----------|---------------|-------------|---------------|

| FLASH_A0  | AG12          | FLASH_D0    | AD19          |

| FLASH_A1  | K12           | FLASH_D1    | AE19          |

| FLASH_A2  | K13           | FLASH_D2    | AE17          |

| FLASH_A3  | H23           | FLASH_D3    | AF16          |

| FLASH_A4  | G23           | FLASH_D4    | AD20          |

| FLASH_A5  | H12           | FLASH_D5    | AE21          |

| FLASH_A6  | J12           | FLASH_D6    | AE16          |

| FLASH_A7  | K22           | FLASH_D7    | AF15          |

| FLASH_A8  | K23           | FLASH_D8    | AH13          |

| FLASH_A9  | K14           | FLASH_D9    | AH14          |

| FLASH_A10 | L14           | FLASH_D10   | AH19          |

| FLASH_A11 | H22           | FLASH_D11   | AH20          |

| FLASH_A12 | G22           | FLASH_D12   | AG13          |

| FLASH_A13 | J15           | FLASH_D13   | AH12          |

| FLASH_A14 | K16           | FLASH_D14   | AH22          |

| FLASH_A15 | K21           | FLASH_D15   | AG22          |

| FLASH_A16 | J22           |             |               |

| FLASH_A17 | L16           | FLASH_CE#   | AE14          |

| FLASH_A18 | L15           | FLASH_WE#   | AF20          |

| FLASH_A19 | L20           | FLASH_OE#   | AF14          |

| FLASH_A20 | L21           | FLASH_RST#  | T24           |

| FLASH_A21 | AE23          | FLASH_BYTE# | AF21          |

| FLASH_A22 | AE12          | FLASH_WAIT  | P25           |

| FLASH_A23 | AE13          | FLASH_ADV#  | N25           |

| FLASH_A24 | AE22          | FLASH_CLK   | R24           |

| FLASH_A25 | AF23          |             |               |

## Table 16 - Flash Interface Pin Assignments

#### 2.4 Clock Sources

The Virtex-5 LXT/SXT PCI Express board includes all of the necessary clocks on the board to implement high-speed logic and RocketIO transceiver designs as well as providing the flexibility for the user to supply their own application specific clocks. The clock sources described in this section are used to derive the required clocks for the memory and communications devices, and the general system clocks for the logic design. This section also provides information on how to supply external user clocks to the FPGA via the on-board connectors and oscillator socket. For a description of the GTP reference clock sources, see <u>Section 2.2.1</u>.

The following figure shows the clock nets connected to the I/O banks containing the global clock input pins on the Virtex-5 LXT/SXT FPGA. Sixteen out of the twenty global clock inputs of the Virtex-5 FPGA are utilized on the board. However the majority of these inputs are for expansion clocks and user inputs. It should be noted that single-ended clock inputs must be connected to the P-side of the pin pair because a direct connection to the global clock tree only exists on this pin. The I/O voltages (VCCO) for the two FPGA banks containing the global clock input pins (Banks 3 and 4) are jumper selectable to either 2.5V or 3.3V. In order to use the differential clock inputs as LVDS inputs, the VCCO voltage for the corresponding bank must be set for 2.5V since the Virtex-5 FPGA does not support 3.3V differential signaling. Single-ended clock inputs do not have this restriction and may be either 2.5V or 3.3V. The interface clocks coming from 3.3V devices on the board are level-shifted to the appropriate VCCO voltage by CB3T standard logic devices prior to the Virtex-5 input pins. Setting both of the voltage selection jumpers to 2.5V (default condition) enables the board to support both single-ended and differential clock inputs.

Figure 11 - Clock Nets Connected to Global Clock Inputs

The on-board 100MHz oscillator provides the system clock input to the global clock tree. This single-ended, 100MHz clock can be used in conjunction with the Virtex-5 Clock Management Tiles (CMTs) to generate the various logic clocks and the clocks forwarded to the DDR2 SDRAM devices. The interface clocks supplied by the communications devices are derived from dedicated crystal oscillators.

| Reference# | Frequency | Derived Interface Clock | Derived Frequency | Virtex-5 pin# |

|------------|-----------|-------------------------|-------------------|---------------|

| U40        | 100 MHz   | CLK_100MHZ              | 100 MHz           | H17           |

| Y1         | 24 MHz    | USB_IFCLK               | 30, 48 MHz        | K31           |

| Y2         | 25 MHz    | CLK_SYNTH0_P            | 25 – 700 MHz      | E4            |

|            |           | CLK_SYNTH0_N            |                   | D4            |

|            |           | CLK_SYNTH0_1P           |                   | AL5           |

|            |           | CLK_SYNTH0_1N           |                   | AL4           |

| Y3         | 25 MHz    | GMII_AUX_RX_CLK         | 2.5, 25 MHz       | AH18          |

|            |           | GMII_AUX_TX_CLK         |                   | AF18          |

|            |           | GBE_AUX_MCLK            | 125 MHz           | AH17          |

| Y4         | 25 MHz    | CLK_SYNTH1_P            | 25 – 700 MHz      | D8            |

|            |           | CLK_SYNTH1_N            |                   | C8            |

|            |           | CLK_SYNTH1_1P           |                   | AL7           |

|            |           | CLK_SYNTH1_1N           |                   | AM7           |

| Y5         | 25 MHz    | GMII_FP_RX_CLK          | 2.5, 25 MHz       | G15           |

|            |           | GMII_FP_TX_CLK          |                   | K18           |

|            |           | GBE_FP_MCLK             | 125 MHz           | K17           |

Table 17 - On-Board Clock Sources

In addition to the 100MHz oscillator, an 8-pin DIP clock socket is provided on the board so the user can supply their own oscillator of choice. The socket is a single-ended, LVTTL or LVCMOS compatible clock input to the FPGA that can be used as an alternate source for the system clock.

| Signal Name | Socket pin# |

|-------------|-------------|

| Enable      | 1           |

| GND         | 4           |

| Output      | 5           |

| VDD         | 8           |

Table 18 - Clock Socket "U23" Pin-out

There are two pairs of SMA connectors for user supplied differential clocks. The first pair is connected to the dedicated GTP clock input pins to provide a reference clock to the transceivers as shown in Figure 4 in <u>Section 2.3</u>. The reference designators for these connectors are "J13" and "J14". The silk screen labels indicate the polarity of the inputs with a trailing minus sign for the N pin and a positive sign for the P pin. These differential clock inputs are AC coupled to the Virtex-5 MGTREFCLK\_116 pins. The other pair of SMA connectors is connected to global clock input pins for general purpose use. The P-side connector could alternatively be used for a single-ended clock. If supplying a differential clock to the SMA connectors labeled "J11" and "J12", make sure the jumper on "JP19" is set for 2.5V and limit the peak-to-peak voltage to 2.5V.

| Net Name   | Input Type   | Connector.pin# | Virtex-5 pin# |

|------------|--------------|----------------|---------------|

| CLK_SOCKET | Global clock | U23.5          | J14           |

| GREFCLK_P  | Global clock | J11.1          | H19           |

| GREFCLK_N  |              | J12.1          | H20           |

| CLK_SMA_N  | GTP clock    | J13.1          | H3            |

| CLK_SMA_P  |              | J14.1          | H4            |

Table 19 - User Clock Inputs

#### 2.4.1 ICS8442 Programmable LVDS Clock Synthesizer

The Virtex-5 LXT/SXT PCI Express development board design uses the ICS8442 LVDS frequency synthesizer for generating various clock frequencies. A list of features included in the ICS8442 device is shown below.

- Output frequency range: 25MHz to 700MHz

- RMS period jitter: 2.7ps (typical)

- Cycle-to-cycle jitter: 27ps (typical)

- Output rise and fall time: 650ps (maximum)

- Output duty cycle: 48/52

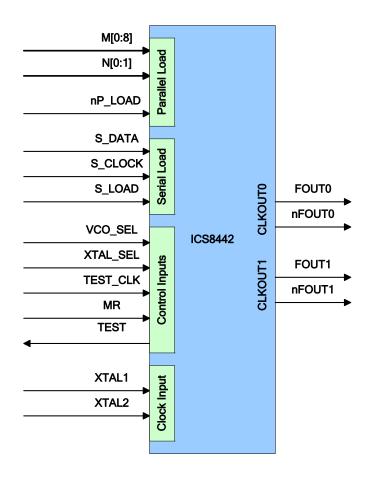

The following figure shows a high-level block diagram of the ICS8442 programmable LVDS clock synthesizer.

| Signal Name    | Direction | Pull up/Pull down | Description                                                                                                               |

|----------------|-----------|-------------------|---------------------------------------------------------------------------------------------------------------------------|

| M[0:4], M[6:8] | Input     | Pull down         | The M divider inputs, latched on the rising edge                                                                          |

| M[5]           | Input     | Pull up           | of the nP_LOAD signal.                                                                                                    |

| N[0:1]         | Input     | Pull down         | The N divider inputs, latched on the rising edge of the nP_LOAD signal.                                                   |

| TEST           | Output    |                   | The TEST output is active during the serial mode<br>of operations. Please refer to the datasheet for<br>more information. |

| MR             | Input     | Pull down         | Active high reset signal.                                                                                                 |

| S_CLOCK        | Input     | Pull down         | Serial interface clock input. Data is shifted into the device on the rising edge of this clock.                           |

| S_DATA         | Input     | Pull down         | Serial interface data input.                                                                                              |

| S_LOAD         | Input  | Pull down | Serial interface load signal. The contents of the serial data shift register is loaded into the internal dividers on the rising edge of this signal.                                                        |

|----------------|--------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TEST_CLK       | Input  | Pull down | Test clock input.                                                                                                                                                                                           |

| nP_LOAD        | Input  | Pull down | The rising edge of this signal is used to load the M and N divider inputs into the device.                                                                                                                  |

| XTAL1, XTAL2   | Input  |           | Crystal clock input/output                                                                                                                                                                                  |

| XTAL_SEL       | Input  | Pull up   | This signal is used to select between the crystal<br>and the TEST_CLK input to the device. When<br>this high, crystal is selected.                                                                          |

| VCO_SEL        | Input  | Pull up   | This signal is used to place the internal PLL in<br>the bypass mode. When this signal is set to low,<br>the PLL is placed in the bypass mode. For<br>normal operations, this signal must be set to<br>high. |

| FOUT0, FOUT1   | Output |           | Positive LVDS clock outputs                                                                                                                                                                                 |

| nFOUT0, nFOUT1 | Output |           | Negative LVDS clock outputs                                                                                                                                                                                 |

Table 20 - ICS8442 Clock Synthesizer Pin Description

The Input Clock Select signals of the ICS8442, "VCO\_SEL" and "XTAL\_SEL", are not used on the Virtex-5 LXT/SXT PCI Express board. The internal pull-ups of these pins put the ICS8842 in normal operation mode where the 25MHz crystal is used as the reference clock to generate the output clocks. None of the serial input control signals are connected on the board. Programming the ICS8442 device is only possible using the M/N DIP switches on the board as indicated in the following sections.

## 2.4.1.1 ICS8442 Clock Generation

The ICS8442 output clocks are generated based on the following formula (assuming the crystal clock input is set to 25MHz):

Where 8 < M < 28 and N can take a value of 1, 2, 4, or 8. The variable M is determined by setting the binary number M[0:8] while N is set according to the following table:

| N[1:0] | Ν | Output Clock Frequency Range (MHz) |         |  |

|--------|---|------------------------------------|---------|--|

|        |   | Minimum                            | Maximum |  |

| 00     | 1 | 200                                | 700     |  |

| 01     | 2 | 100                                | 350     |  |

| 10     | 4 | 50                                 | 175     |  |

| 11     | 8 | 25                                 | 87.5    |  |

#### Table 21 - ICS8442 N Settings

For example, to generate a 62.5MHz clock, N[1:0] will be set to "10" (it can also be set to "11" since either one will be the correct frequency range for the 62.5MHz clock) and M will be set to "000001010" (decimal 10). So, from the above formula:

The following table shows how the M and N values can be set to generate a clock source for a few common applications. All the values for M and N are based on the 25MHz crystal clock input to the ICS8442 device. A complete list of frequencies generated by the ICS8442 (based on a 25MHz input clock) is provided in the following sections.

| Interconnect     | FOUT0 and   | ICS8442 M and N Settings |    |    |    |    |    |    |    |    |    |    |

|------------------|-------------|--------------------------|----|----|----|----|----|----|----|----|----|----|

| Technology       | FOUT1 (MHz) | M8                       | M7 | M6 | M5 | M4 | M3 | M2 | M1 | MO | N1 | N0 |

| Gigabit Ethernet | 125         | 0                        | 0  | 0  | 0  | 0  | 1  | 0  | 1  | 0  | 0  | 1  |

| Fiber Channel    | 106.25      | 0                        | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 1  | 1  | 0  |

|                  | 212.5       | 0                        | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 1  | 0  | 1  |

| Infiniband       | 250         | 0                        | 0  | 0  | 0  | 0  | 1  | 0  | 1  | 0  | 0  | 0  |

| XAUI             | 312.5       | 0                        | 0  | 0  | 0  | 1  | 1  | 0  | 0  | 1  | 0  | 1  |

Table 22 - Examples of the ICS8442 M and N Settings

#### 2.4.1.2 ICS8442 M and N Settings

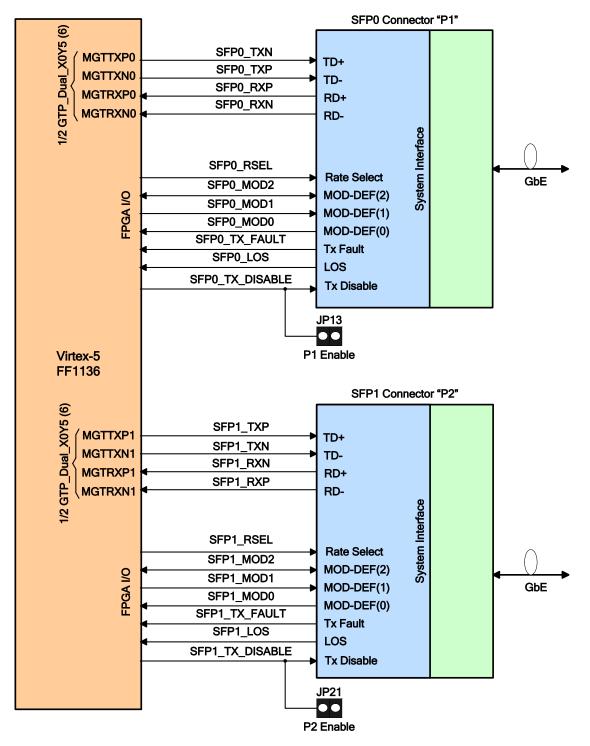

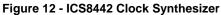

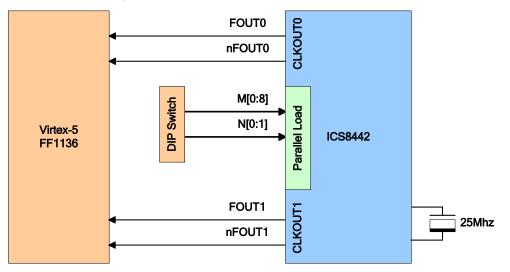

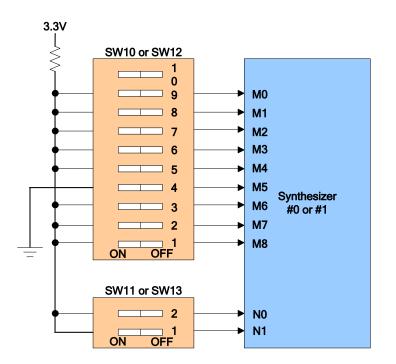

The following figure shows how the ICS8442 programmable LVDS clock synthesizer is used on the Virtex-5 LXT/SXT PCI Express board. To limit the number of required Virtex-5 I/O pins, only Parallel Mode is supported. DIP switches are provided on the board for the manual setting of the M and N values for each ICS8442.

Figure 13 - ICS8442 Clock Synthesizer Interface to the FPGA